Hi, I have been bringing up a new cape design and am having problems with the 16 boot pin signals. I have designed a circuit which uses two 74LVC245 chips to tri-state the lines during boot up. I’m using the SYS_RESETn line (with an inverter) as the OE*. However, when I captured the SYS_RESETn line on my logic analyzer, it appears to be changing states a couple of times during bootup. I’m still not able to bootup and wanted to confirm that this signal is correct.

Thanks!

SYS_RESET has nothing to do with the boot pins. It is just a way to insure it is there for a while and no longer using a signal that is on the expansion headers. The PORZn pin is the one that latches the data.

I would be more interested in looking at your schematic your schematic.

Gerald

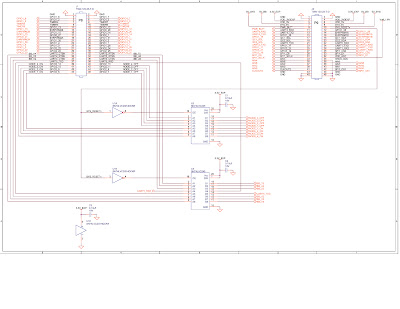

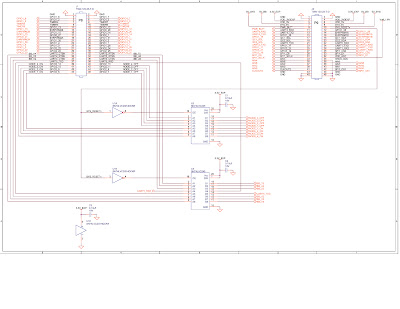

Hi Gerald - Thanks for the response. Attached is a picture of the relevant circuit. I saw another cape board that had done something similar. I am trying to hold those 16 pins in tri-state during the bootup process. I believe this is what I need to do but please correct me if I am wrong.

Thanks!

Chad

SYS_RESTn is active low. You need to remove the inverters. You want the outputs enabled during the reset period.

Gerald