Hi,

I am trying to build the BeagleV-Fire / Gateware · GitLab project using the default python3 build-bitstream.py ./build-options/default.yaml command. I’m using Libero 2024.1.

I’m on the latest from main, 6e31fb5 though I also tried 0.5.1. Last year I could build this project without issues, so I’m not sure what changed.

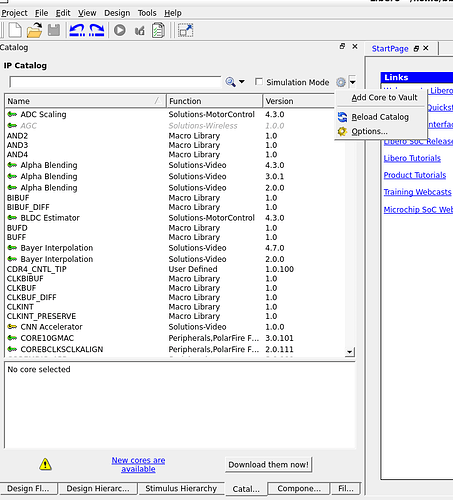

It appears that the .tcl script is trying to set options for PF_CCC:2.2.220 that aren’t supported by the core, but I suspect something else is wrong, since this script and this version of Libero have been tested together, and the PF_CCC version is dated 2022 when I looked it up on Microchip’s website. I’m hoping someone can help me understand this.

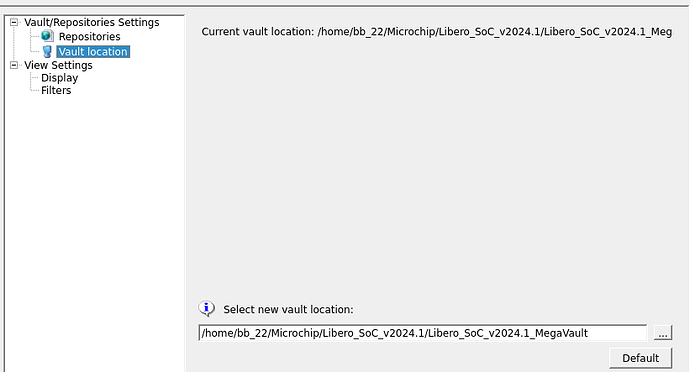

I installed Libero to /opt/microchip/, but I’ve updated all of the paths in my .bashrc to point to the install similar to the instructions in Microchip FPGA Tools Installation Guide — BeagleBoard Documentation.

================================================================================

Generate Libero project

================================================================================

top level name: DEFAULT_6E31FB50E3CF28D90FAC95

Console Mode = Libero v2024.1 detected.

Setting parameter BOARD to mpfs-beaglev-fire

Setting parameter DIE to MPFS025T

Setting parameter PACKAGE to FCVG484

Setting parameter DIE_VOLTAGE to 1.0

Setting parameter PART_RANGE to EXT

Setting parameter PROJECT_LOCATION to ../.././work/libero

Setting parameter TOP_LEVEL_NAME to DEFAULT_6E31FB50E3CF28D90FAC95

Setting parameter HSS_IMAGE_PATH to ../../work/HSS/hss-envm-wrapper-bm1-p0.hex

Setting parameter PROG_EXPORT_PATH to ../../.

Setting parameter DESIGN_VERSION to 2004

Cape options selected: DEFAULT

M.2 option selected: DEFAULT

SYZYGY high speed connector option option selected: DEFAULT

MIPI CSI option option selected: DEFAULT

PROJECT_LOCATION: ../.././work/libero

DESIGN_VERSION: 2004

SILICON_SIGNATURE: bea913b0

BOARD: mpfs-beaglev-fire

DIE: MPFS025T

PACKAGE: FCVG484

DIE_VOLTAGE: 1.0

PART_RANGE: EXT

Info: This version of Libero supports only the enhanced constraint flow.

The BVF_GATEWARE_025T project was created.

Downloading Actel:SgCore:PF_OSC:1.0.102...

Info: Core 'Actel:SgCore:PF_OSC:1.0.102' was successfully downloaded.

Downloading Actel:SgCore:PF_CCC:2.2.220...

Info: Core 'Actel:SgCore:PF_CCC:2.2.220' was successfully downloaded.

Downloading Actel:DirectCore:CORERESET_PF:2.3.100...

Info: Core 'Actel:DirectCore:CORERESET_PF:2.3.100' was successfully downloaded.

Downloading Microsemi:SgCore:PFSOC_INIT_MONITOR:1.0.307...

Info: Core 'Microsemi:SgCore:PFSOC_INIT_MONITOR:1.0.307' was successfully downloaded.

Downloading Actel:DirectCore:COREAXI4INTERCONNECT:2.8.103...

Info: Core 'Actel:DirectCore:COREAXI4INTERCONNECT:2.8.103' was successfully downloaded.

Downloading Actel:SgCore:PF_CLK_DIV:1.0.103...

Info: Core 'Actel:SgCore:PF_CLK_DIV:1.0.103' was successfully downloaded.

Downloading Actel:SgCore:PF_DRI:1.1.104...

Info: Core 'Actel:SgCore:PF_DRI:1.1.104' was successfully downloaded.

Downloading Actel:SgCore:PF_NGMUX:1.0.101...

Info: Core 'Actel:SgCore:PF_NGMUX:1.0.101' was successfully downloaded.

Downloading Actel:SgCore:PF_PCIE:2.0.121...

Info: Core 'Actel:SgCore:PF_PCIE:2.0.121' was successfully downloaded.

Downloading Actel:SgCore:PF_TX_PLL:2.0.304...

Info: Core 'Actel:SgCore:PF_TX_PLL:2.0.304' was successfully downloaded.

Downloading Actel:SgCore:PF_XCVR_REF_CLK:1.0.103...

Info: Core 'Actel:SgCore:PF_XCVR_REF_CLK:1.0.103' was successfully downloaded.

Downloading Actel:DirectCore:CoreAPB3:4.2.100...

Info: Core 'Actel:DirectCore:CoreAPB3:4.2.100' was successfully downloaded.

Downloading Actel:DirectCore:CoreGPIO:3.2.102...

Info: Core 'Actel:DirectCore:CoreGPIO:3.2.102' was successfully downloaded.

Downloading Actel:SystemBuilder:PF_SRAM_AHBL_AXI:1.2.108...

Info: Core 'Actel:SystemBuilder:PF_SRAM_AHBL_AXI:1.2.108' was successfully downloaded.

Downloading Actel:Simulation:CLK_GEN:1.0.1...

Info: Core 'Actel:Simulation:CLK_GEN:1.0.1' was successfully downloaded.

Downloading Actel:Simulation:RESET_GEN:1.0.1...

Info: Core 'Actel:Simulation:RESET_GEN:1.0.1' was successfully downloaded.

Downloading Actel:DirectCore:corepwm:4.5.100...

Info: Core 'Actel:DirectCore:corepwm:4.5.100' was successfully downloaded.

Downloading Actel:DirectCore:COREI2C:7.2.101...

Info: Core 'Actel:DirectCore:COREI2C:7.2.101' was successfully downloaded.

Downloading Actel:DirectCore:CoreUARTapb:5.7.100...

Info: Core 'Actel:DirectCore:CoreUARTapb:5.7.100' was successfully downloaded.

Downloading Actel:SystemBuilder:PF_IOD_GENERIC_RX:2.1.110...

Info: Core 'Actel:SystemBuilder:PF_IOD_GENERIC_RX:2.1.110' was successfully downloaded.

Downloading Actel:SgCore:PF_IO:2.0.105...

Info: Core 'Actel:SgCore:PF_IO:2.0.105' was successfully downloaded.

Downloading Actel:SystemBuilder:PF_XCVR_ERM:3.1.205...

Info: Core 'Actel:SystemBuilder:PF_XCVR_ERM:3.1.205' was successfully downloaded.

Downloading Microchip:SolutionCore:mipicsi2rxdecoderPF:4.7.0...

Info: Core 'Microchip:SolutionCore:mipicsi2rxdecoderPF:4.7.0' was successfully downloaded.

MSS filename: PF_SOC_MSS

Info: Design 'PF_SOC_MSS' was successfully imported.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/component/work/PF_SOC_MSS/PF_SOC_MSS.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/component/work/PF_SOC_MSS/MSS_NOBYP_NOBYP_NOBYP_BYP_BYP_syn_comps.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/hdl/apb_arbiter.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/hdl/AXI4_address_shim.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/hdl/miv_ihcc.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/hdl/miv_ihcc_ctrl.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/hdl/miv_ihcc_irqs.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/hdl/miv_ihcc_mem.v'.

Reading file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/hdl/miv_ihcia.v'.

Info: Core has been created successfully from 'APB_ARBITER' HDL module.

Info: <a href="liberoaction://open_online_help/70004">Read more</a> on how to create a core from your HDL module.

Info: This feature enables you to add bus interfaces to your HDL module and configure any generics/parameters in your HDL module.

Info: Core has been created successfully from 'MIV_IHCC' HDL module.

Info: <a href="liberoaction://open_online_help/70004">Read more</a> on how to create a core from your HDL module.

Info: This feature enables you to add bus interfaces to your HDL module and configure any generics/parameters in your HDL module.

Info: Core has been created successfully from 'MIV_IHCIA' HDL module.

Info: <a href="liberoaction://open_online_help/70004">Read more</a> on how to create a core from your HDL module.

Info: This feature enables you to add bus interfaces to your HDL module and configure any generics/parameters in your HDL module.

Info: Core has been created successfully from 'AXI_ADDRESS_SHIM' HDL module.

Info: <a href="liberoaction://open_online_help/70004">Read more</a> on how to create a core from your HDL module.

Info: This feature enables you to add bus interfaces to your HDL module and configure any generics/parameters in your HDL module.

Info: 'CORERESET' was successfully generated.

Info: 'CORERESET' manifest file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/component/work/CORERESET/CORERESET_manifest.txt' was successfully generated.

Info: Component 'CORERESET' was successfully created and configured with vendor:Actel library:DirectCore name:CORERESET_PF version:2.3.100.

Info: 'INIT_MONITOR' was successfully generated.

Info: 'INIT_MONITOR' manifest file '/home/sstel/workspace/polarfire/beaglev-fire-gateware/work/libero/component/work/INIT_MONITOR/INIT_MONITOR_manifest.txt' was successfully generated.

Info: Component 'INIT_MONITOR' was successfully created and configured with vendor:Microsemi library:SgCore name:PFSOC_INIT_MONITOR version:1.0.307.

Error: SmartDesign 'FPGA_CCC_C0' design rules check failed

Error: Design rules check of "FPGA_CCC_C0" failed.

Check the log window for more information.

[OK]

Error: 'Incompatible Family Configuration' :

Warning: 'Core Validation' : PLL_FEEDBACK_MODE_0 If you select Post-VCO as a Feedback Mode, outputs will be resynchronized between each other after the PLL locks, but will not be resynchronized with the PLL reference clock

Info: 'Core Validation' : Incorrect PLL_LOCK_COUNT value of 0 found, updating the value to be 8.

Info: 'Core Validation' : The current configuration of instance : FPGA_CCC_C0_0 has warning or information messages. Consult the User Guide for configuration of this core.

Error: Could not configure component 'FPGA_CCC_C0'.

Error: The command 'create_and_configure_core' failed.

============= SCRIPT EXECUTION ERROR =============

Script: script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl

Error Message:

File: script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl

Line: 5

Depth: 1

Caller file and line number not available

Stack Trace:

while executing

"create_and_configure_core -core_vlnv {Actel:SgCore:PF_CCC:*} -component_name {FPGA_CCC_C0} -params {\

"DLL_CLK_0_BANKCLK_EN:false" \

"DLL_CLK_0_DEDIC..."

(file "script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl" line 5)

invoked from within

"source script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl"

("uplevel" body line 1)

invoked from within

"uplevel #0 [list source $script]"

=================================================

============= SCRIPT EXECUTION ERROR =============

Script: ./script_support/B_V_F_recursive.tcl

Error Message:

File: script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl

Line: 5

Depth: 1

Caller File: ./script_support/B_V_F_recursive.tcl

Caller Line: 18

Depth: 2

Stack Trace:

while executing

"create_and_configure_core -core_vlnv {Actel:SgCore:PF_CCC:*} -component_name {FPGA_CCC_C0} -params {\

"DLL_CLK_0_BANKCLK_EN:false" \

"DLL_CLK_0_DEDIC..."

(file "script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl" line 5)

invoked from within

"source script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl"

("uplevel" body line 1)

invoked from within

"uplevel #0 [list source $script]"

(procedure "::safe_source" line 6)

invoked from within

"::safe_source script_support/components/CLOCKS_AND_RESETS/FPGA_CCC_C0.tcl"

(file "./script_support/B_V_F_recursive.tcl" line 18)

invoked from within

"source ./script_support/B_V_F_recursive.tcl"

("uplevel" body line 1)

invoked from within

"uplevel #0 [list source $script]"

=================================================

Error: Failure when executing Tcl script. [ Line 263 ]

Error: The Execute Script command failed.

The BVF_GATEWARE_025T project was closed.

Finished