I’m using the CAPE_4_UARTS cape option, and in the device tree overlay file, I see that there are 4 UARTS specified as follows:

&mmuart1 {

status = "okay";

symlink = "bone/uart/5";

};

&mmuart2 {

status = "okay";

symlink = "bone/uart/1";

};

&mmuart3 {

status = "okay";

symlink = "bone/uart/2";

};

&mmuart4 {

status = "okay";

symlink = "bone/uart/4";

};

However, when I do the build, I only see three of them show up as valid ports in /dev/bone/uart:

beagle@BeagleV:/dev/bone/uart$ ll

total 4

drwxr-xr-x 2 root root 120 Mar 18 19:32 ./

drwxr-xr-x 7 root root 140 Mar 18 19:32 ../

lrwxrwxrwx 1 root root 11 Sep 19 2023 1 -> ../../ttyS2

lrwxrwxrwx 1 root root 11 Sep 19 2023 2 -> ../../ttyS3

lrwxrwxrwx 1 root root 11 Sep 19 2023 5 -> ../../ttyS1

-rw-r--r-- 1 root root 344 Mar 18 19:32 README.md

beagle@BeagleV:/dev/bone/uart$

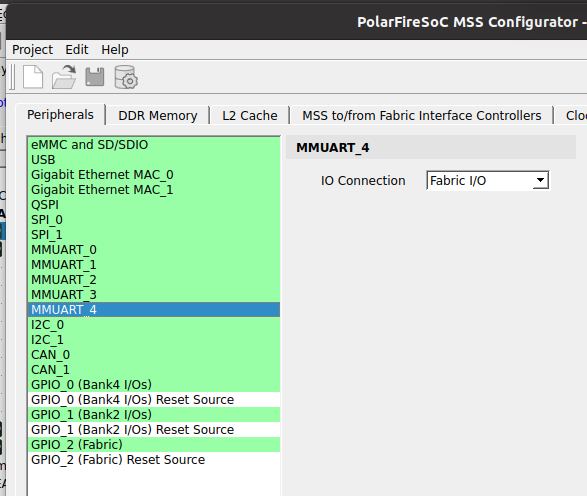

I have looked in the Libero project, and it appears to me that all 4 UARTS that route through FPGA fabric (MMUART_1 through MMUART_4) are enabled, and are routed to the pins as expected:

The three UARTs that show up are working as expected. Is there something else I need to do to get the fourth UART working?