I'm attempting to put the Bone into SLEEP state, as defined by the

TPS65217, where only LDO1 stays active but all other power rails turn

off. I want to do this so I can keep the real time clock running in

the AM335x but not consume much power.

I am not trying to do any kind of suspend to ram or hibernation.

The default setting for the TPS65217 STATUS REGISTER (register 0x0A)

bit 7 is "0" which should put the TPS65217 into SLEEP mode when PWR_EN

(same net as PMIC_POWER_EN from the AM335x) is pulled low.

I pull the PMIC_POWER_EN pin low by causing an ALARM2 condition within

the AM335x real time clock module. When I set the TPS65217 STATUS

REGISTER bit 7 to "1" and then pull PMIC_POWER_EN low, I can

successfully enter OFF mode. Exiting OFF mode (ie: powering up) is

accomplished by inserting either USB or AC power while maintaining

input power to the TPS65217 (either by using the other one than I'm

plugging, or via lithium battery on P6) or by pushing the power button

(on P9). But unless I perform one of these actions, the TPS65217 stays

OFF, rather successfully. But OFF mode disables LDO1 meaning my real

time clock forgets what time it is, thus, I want to use SLEEP mode.

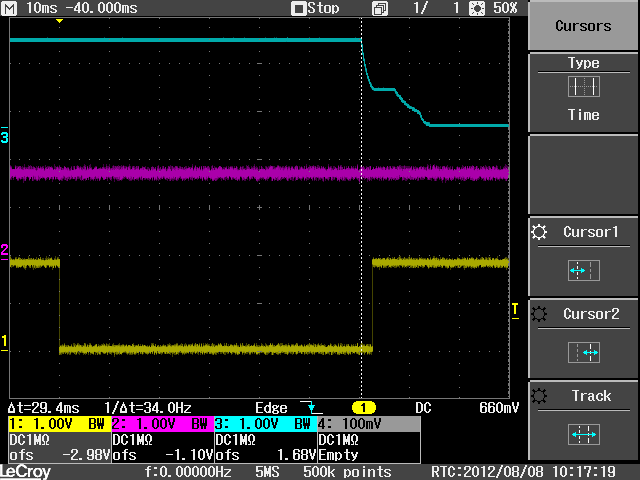

But, when I attempt to enter SLEEP mode, I'm able to enter it, but then

the TPS65217 powers right back up. I'm seeing the PMIC_POWER_EN line

from the AM335x going low because of the ALARM2, but then 60 ms later,

it goes high again. I assume this is because the PMIC_POWER_EN I/O

goes to high-z pulled-up state while in reset (the data sheet doesn't

say what the state of pins are when the AM335x is off, just during

and post-reset, so I assume powered off state is the same as reset

state).

There's no pull-down on the PMIC_POWER_EN line to counteract the weak

pull-up that is internal to the AM335x (at least during reset, but

probably during power off, too). Possibly having a pull-down here would

cause the Bone to never power up under some circumstances, but I've not

attempted to rework one this way, yet.

In OFF mode, the TPS65217 won't wake except for power button or the

rising edge of a power source. But in SLEEP mode, the TPS65217 will

wake because of PWR_EN going high or any of the conditions to wake from

OFF mode. Because of this, I'd like PMIC_POWER_EN to stay low unless

being driven by the AM335x to be high.

Is this possible? Or am I most likely doing something else wrong? Am

I forgetting a register setting in the TPS65217?

Has any one had success getting the TPS65217 to enter SLEEP mode on the

Bone?

Thanks,

Andrew

Have a good Olympics.

Have a good Olympics.