TLDR:

Assuming LAN8710 datasheet is correct, then previously the phy reset was implemented in an out-of-spec way, so just a single (compliant) reset signal should be sufficient. It looks to me like this might not happen unless the new GPIO (as implemented on C3 boards) is used.

The following could do with checking…

The following are relevant references:

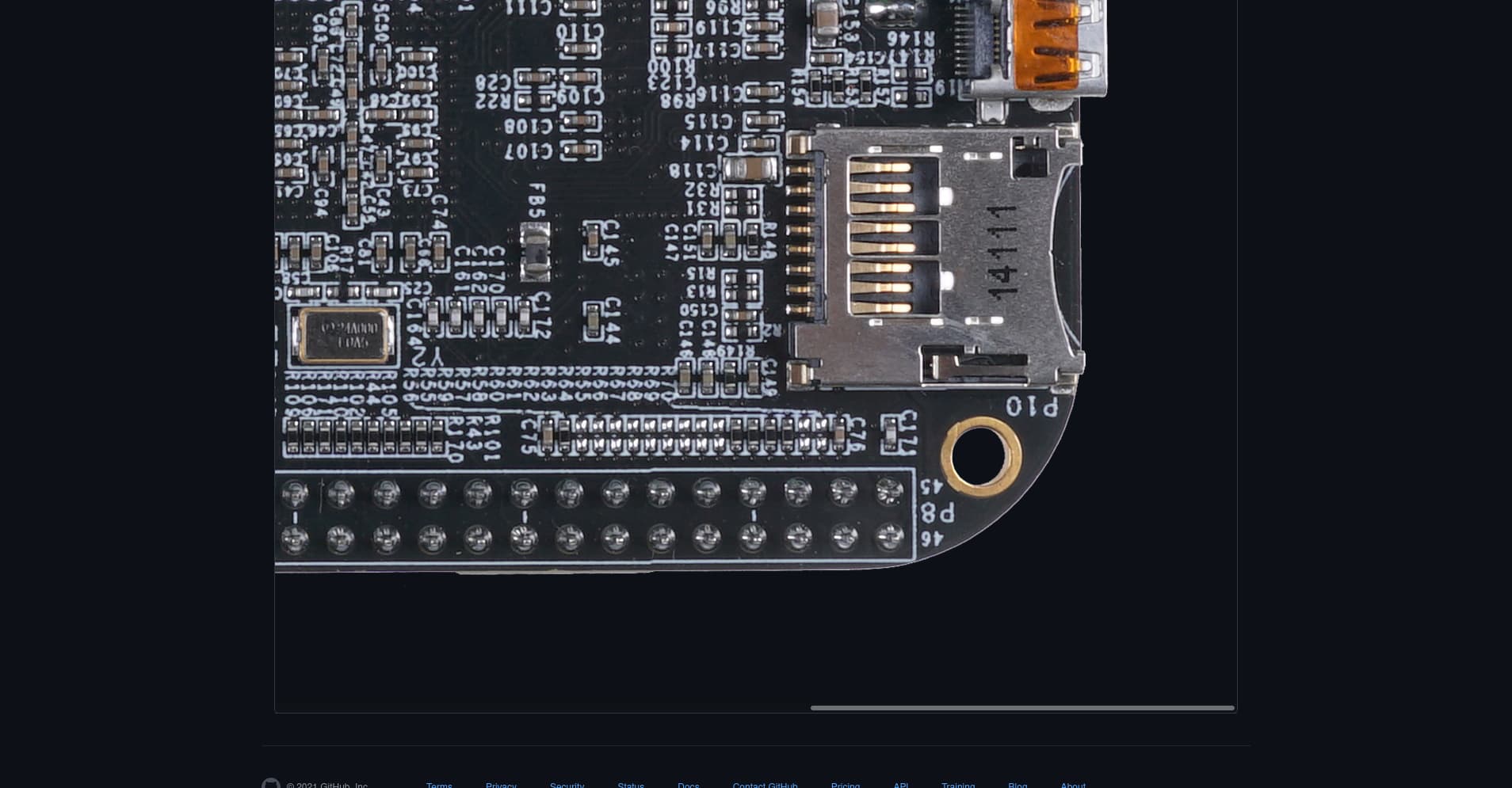

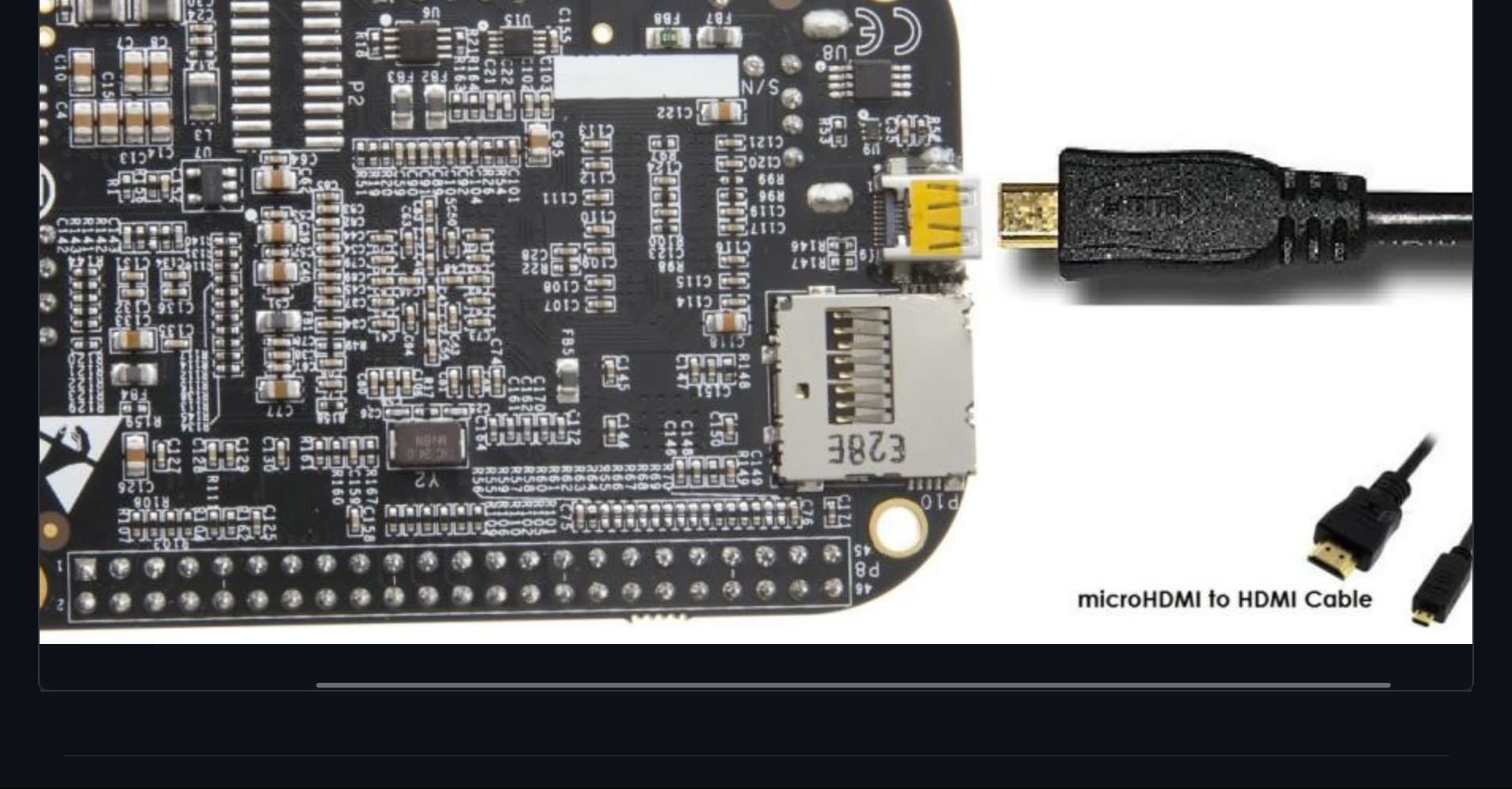

Schematic for new C3 revision BBB is part of this commit (file BBB_SCH.pdf):

The schematic for the revised board is here as BBB_SCH.pdf:

See changelog entry at bottom of sheet 1…

On page 9, the PHY reset line is now asserted (held low) when either the sys reset signal is low, OR when GPIO1_8 is low (due to the AND gate in the new U1 IC at the bottom of sheet 9).

The AND gate U1 has Schmitt triggers on its inputs, so the length of the assertion of the PHY reset signal is due to the time that GPIO1_8 is held low, and the effect of the new RC network C174 - 4.7 µF - and R33 - 10kΩ.

Datasheet for the Microchip LAN8710A

nRST is a variable-voltage schmitt triggered input with an internal 50µA pull-up (page 12 (table 2-5), page 14 (table 2-9) and which gets de-asserted when it’s input signal rises above a threshold of somewhere between 0.81v and 1.9v (typical 1.65v for the BBB’s 3.3v supply).

Reset signal timing requirements are on page 59 and 60 (section 5.5.3).

In [Resolved] AM3358: BBB reboot issue with Ethernet PHY - Sitara Processors Forum - Sitara™ Processors - TI E2E Community the problem is described by a TI employee as “the AM335X nRESET_INOUT (or warm reset) is released at approximately the moment that the PHY latches internally it’s bootstrap resistors. Once in a while this happens too soon and the PHY doesn’t come out of reset correctly. This can be avoided if the PHY reset is tied to a processor GPIO (it’s important that the GPIO stays in low state during reset and at reset release time).”

… I think this is saying that the violated requirement was that nRST shouldn’t be released less than 25ms after the power supplies go OK (“tpurstd”).

The sys reset signal is held low until the PMIC power good is asserted, and at that point C24 would start to charge, and the line would reach the LAN8710 min/typical/max trigger voltages (0.81v / 1.65v / 1.9v) after 6.2 / 15.3 / 19.9 ms. These are all less than 25ms.

With the new higher value C174, these min/typical/max values become 13.2 / 32.6 / 40.3 ms.

After 25 ms, the voltage should be 1.36v. This assumes that U1 will pull down to 0v (which it won’t completely do), and also disregards the internal pull-up on nRST both of which will cause the voltage to rise quicker, and so release nRST sooner, and also component value tolerances. Other factors could also be favourable of course.

… but because the worst-case the nRST release time looks like it could still be out of spec if the GPIO is not also used, to be on the safe side, the GPIO1_8 should probably be driven low by the bootloader for min 100 µs anyway.

I’m guessing that the code would run more than 25ms after the processor boots (since uboot would be read from flash, and quite a lot of other early init is probably done first).

If we take the LAN8710 datasheet at face value, then this should be sufficient.

Maybe just implement this initially, and see if anyone reports further problems?

Some reasonable looking tests were also reported to check the IC state, so these could be implemented if further problems are reported?