BBAI-64 USE TI-SDK10.0

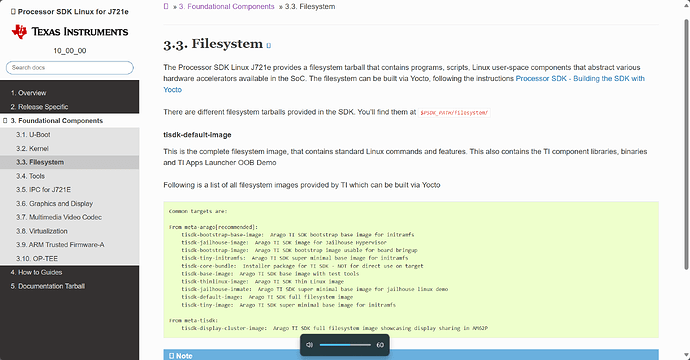

Download SDK

- https://dr-download.ti.com/software-development/software-development-kit-sdk/MD-U6uMjOroyO/10.00.00.08/ti-processor-sdk-linux-adas-j721e-evm-10_00_00_08-Linux-x86-Install.bin

- https://dr-download.ti.com/software-development/software-development-kit-sdk/MD-bA0wfI4X2g/10.00.00.05/ti-processor-sdk-rtos-j721e-evm-10_00_00_05.tar.gz

build bl31.bin

# linux sdk

cd board-support/trusted-firmware-a-2.10+git/

make CROSS_COMPILE=aarch64-linux-gnu- ARCH=aarch64 PLAT=k3 TARGET_BOARD=generic SPD=opteed K3_USART=0x0 -j12

cd -

build bl32.bin

cd board-support/optee-os-4.2.0+git/

make CROSS_COMPILE=arm-linux-gnueabihf- CROSS_COMPILE64=aarch64-linux-gnu- CFG_CONSOLE_UART=0x0 PLATFORM=k3-j721e CFG_ARM64_core=y -j12

cd -

cp board-support/optee-os-4.2.0+git/out/arm-plat-k3/core/tee-pager_v2.bin board-support/prebuilt-images/bl32.bin

modify Rules.make

#u-boot machine

# UBOOT_MACHINE=j721e_evm_a72_config

UBOOT_MACHINE=j721e_beagleboneai64_a72_defconfig

# Add CROSS_COMPILE and UBOOT_MACHINE for the R5

# UBOOT_MACHINE_R5=j721e_evm_r5_config

UBOOT_MACHINE_R5=j721e_beagleboneai64_r5_defconfig

modify arm64-mmu.c

#if defined (CONFIG_TARGET_J721E_A72_EVM) || defined (CONFIG_TARGET_J721E_A72_BEAGLEBONEAI64)

/* NR_DRAM_BANKS + 32bit IO + 64bit IO + terminator */

#define NR_MMU_REGIONS (CONFIG_NR_DRAM_BANKS + 6)

build u-boot

make u-boot

mv board-support/ti-u-boot-2024.04+git/build/a72/u-boot.img_unsigned board-support/ti-u-boot-2024.04+git/build/a72/u-boot.img

mv board-support/ti-u-boot-2024.04+git/build/a72/tispl.bin_unsigned board-support/ti-u-boot-2024.04+git/build/a72/tispl.bin

make u-boot_install

modify k3-j721e-beagleboneai64.dts

- modify reserved_memory , reference rtos sdk vision_apps/platform/j721e/rtos/k3-j721e-rtos-memory-map.dtsi

- enable r5 core

- example , reference linux sdk board-support/ti-linux-kernel-6.6.32+git-ti/arch/arm64/boot/dts/ti/k3-j721e-rtos-memory-map.dtsi

&main_r5fss0_core0 { status = "okay"; mboxes = <&mailbox0_cluster1>, <&mbox_main_r5fss0_core0>; memory-region = <&vision_apps_main_r5fss0_core0_dma_memory_region>, <&vision_apps_main_r5fss0_core0_memory_region>, <&vision_apps_main_r5fss0_core0_shared_memory_queue_region>, <&vision_apps_main_r5fss0_core0_shared_memory_bufpool_region>; };

build linux

make linux

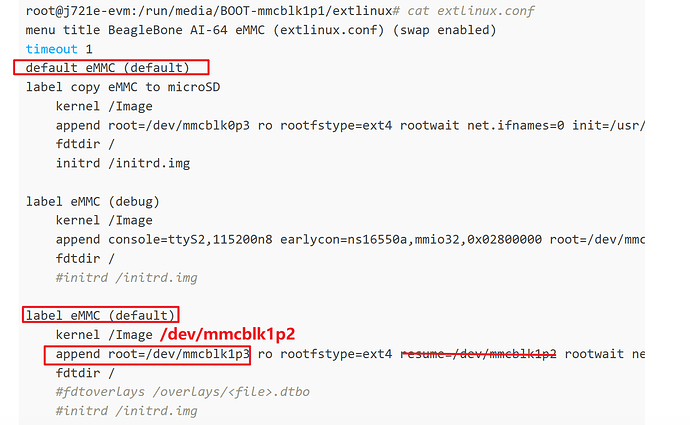

copy boot img to sd card

reference board-support/ti-u-boot-2024.04+git/doc/board/beagle/j721e_beagleboneai64.rst

-rwxrwx--- 1 root disk 20285952 Feb 27 17:43 Image

drwxrwx--- 2 root disk 512 Jul 4 2024 extlinux

-rwxrwx--- 1 root disk 268978 Feb 27 2024 sysfw.itb

drwxrwx--- 2 root disk 512 Feb 27 17:31 ti

-rwxrwx--- 1 root disk 205897 Feb 27 2024 tiboot3.bin

-rwxrwx--- 1 root disk 1027099 Feb 27 2024 tispl.bin

-rwxrwx--- 1 root disk 1014147 Feb 27 2024 u-boot.img

-rwxrwx--- 1 root disk 1515 Feb 27 17:47 uEnv.txt

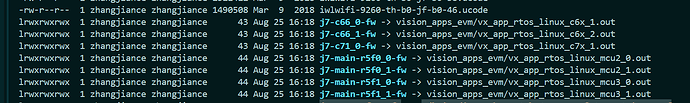

boot and run r5 prog

log like as flow

root@j721e-evm:~# /opt/vision_apps/vision_apps_init.sh

[MCU2_0] 10.280540 s: CIO: Init ... Done !!!

[MCU2_0] 10.280613 s: ### CPU Frequency = 1000000000 Hz

[MCU2_0] 10.280656 s: CPU is running FreeRTOS

[MCU2_0] 10.280678 s: APP: Init ... !!!

[MCU2_0] 10.280698 s: SCICLIENT: Init ... !!!

[MCU2_0] 10.280916 s: SCICLIENT: DMSC FW version [10.0.8--v10.00.08 (Fiery Fox)]

[MCU2_0] 10.280967 s: SCICLIENT: DMSC FW revision 0xa

[MCU2_0] 10.280999 s: SCICLIENT: DMSC FW ABI revision 4.0

[MCU2_0] 10.281029 s: SCICLIENT: Init ... Done !!!

[MCU2_0] 10.281055 s: UDMA: Init ... !!!

[MCU2_0] 10.282167 s: UDMA: Init ... Done !!!

[MCU2_0] 10.282235 s: MEM: Init ... !!!

[MCU2_0] 10.282286 s: MEM: Created heap (DDR_LOCAL_MEM, id=0, flags=0x00000004) @ d9000000 of size 15728640 bytes !!!

[MCU2_0] 10.282362 s: MEM: Created heap (L3_MEM, id=1, flags=0x00000000) @ 3600000 of size 262144 bytes !!!

[MCU2_0] 10.282421 s: MEM: Created heap (DDR_CACHE_WT_MEM, id=7, flags=0x00000000) @ d9f00000 of size 1048576 bytes !!!

[MCU2_0] 10.282475 s: MEM: Init ... Done !!!

[MCU2_0] 10.282500 s: IPC: Init ... !!!

[MCU2_0] 10.282554 s: IPC: 8 CPUs participating in IPC !!!

[MCU2_0] 10.282605 s: IPC: Waiting for HLOS to be ready ... !!!

[MCU2_0] 10.282644 s: IPC: HLOS is ready !!!

[MCU2_0] 10.288664 s: IPC: Init ... Done !!!

[MCU2_0] 10.288733 s: APP: Syncing with 7 CPUs ... !!!

[MCU2_0] 10.910003 s: APP: Syncing with 7 CPUs ... Done !!!

[MCU2_0] 10.910096 s: REMOTE_SERVICE: Init ... !!!

[MCU2_0] 10.910630 s: REMOTE_SERVICE: Init ... Done !!!

[MCU2_0] 10.910709 s: FVID2: Init ... !!!

[MCU2_0] 10.910810 s: FVID2: Init ... Done !!!

start openocd for debug

root@j721e-evm:~# openocd -f vm.cfg

Open On-Chip Debugger 0.12.0+dev-01687-gac63cd00d-dirty (2024-08-18-13:28)

Licensed under GNU GPL v2

For bug reports, read

http://openocd.org/doc/doxygen/bugs.html

Info : only one transport option; autoselecting 'dapdirect_swd'

Info : Listening on port 6666 for tcl connections

Info : Listening on port 4444 for telnet connections

Info : clock speed 2500 kHz

Info : [j721e.cpu.sysctrl] starting gdb server on 3333

Info : Listening on port 3333 for gdb connections

Info : [j721e.cpu.mcu_r5.0] starting gdb server on 3334

Info : Listening on port 3334 for gdb connections

Info : [j721e.cpu.mcu_r5.1] starting gdb server on 3335

Info : Listening on port 3335 for gdb connections

Info : [j721e.cpu.main0_r5.0] starting gdb server on 3336

Info : Listening on port 3336 for gdb connections

Info : [j721e.cpu.main0_r5.1] starting gdb server on 3337

Info : Listening on port 3337 for gdb connections

Info : [j721e.cpu.main1_r5.0] starting gdb server on 3338

Info : Listening on port 3338 for gdb connections

Info : [j721e.cpu.main1_r5.1] starting gdb server on 3339

Info : Listening on port 3339 for gdb connections

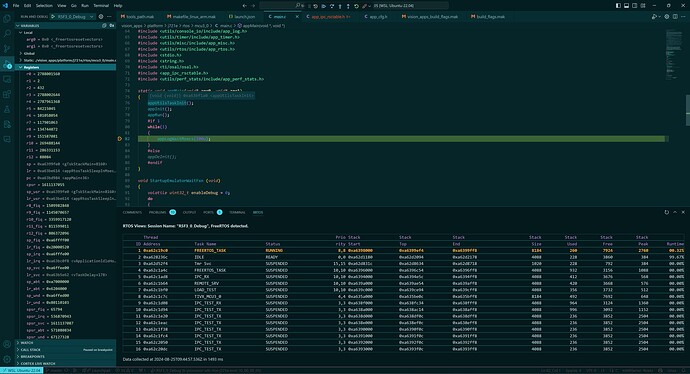

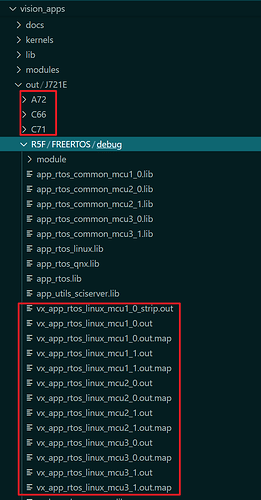

vscode debug

launch.json as flow

{

// Use IntelliSense to learn about possible attributes.

// Hover to view descriptions of existing attributes.

// For more information, visit: https://go.microsoft.com/fwlink/?linkid=830387

"version": "0.2.0",

"configurations": [

{

"name": "R5F2_0_Debug",

"cwd": "${workspaceFolder}",

"executable": "./vision_apps/out/J721E/R5F/FREERTOS/debug/vx_app_rtos_linux_mcu2_0.out",

"request": "attach",

"type": "cortex-debug",

"runToEntryPoint": "main",

"servertype": "external",

"gdbPath":"/usr/bin/gdb-multiarch",

"gdbTarget":"198.18.39.39:3336"

},

{

"name": "R5F2_1_Debug",

"cwd": "${workspaceFolder}",

"executable": "./vision_apps/out/J721E/R5F/FREERTOS/debug/vx_app_rtos_linux_mcu2_1.out",

"request": "attach",

"type": "cortex-debug",

"runToEntryPoint": "main",

"servertype": "external",

"gdbPath":"/usr/bin/gdb-multiarch",

"gdbTarget":"198.18.39.39:3337"

},

{

"name": "R5F3_0_Debug",

"cwd": "${workspaceFolder}",

"executable": "./vision_apps/out/J721E/R5F/FREERTOS/debug/vx_app_rtos_linux_mcu3_0.out",

"request": "attach",

"type": "cortex-debug",

"runToEntryPoint": "main",

"servertype": "external",

"gdbPath":"/usr/bin/gdb-multiarch",

"gdbTarget":"198.18.39.39:3338"

},

{

"name": "R5F3_1_Debug",

"cwd": "${workspaceFolder}",

"executable": "./vision_apps/out/J721E/R5F/FREERTOS/debug/vx_app_rtos_linux_mcu3_1.out",

"request": "attach",

"type": "cortex-debug",

"runToEntryPoint": "main",

"servertype": "external",

"gdbPath":"/usr/bin/gdb-multiarch",

"gdbTarget":"198.18.39.39:3339"

}

]

}